这几年,AMD大打“核战”,在处理器核心数上一路领先,Intel则有些力不从心,拼命堆叠也依然差距不小。

AMD的下一代霄龙代号“Genoa”(热那亚),Zen4架构,将升至96核心192线程,比现在多一半。

Intel的下一代至强代号“Sapphire Rapids”(蓝宝石激流),最多60核心120线程,但实际开启56核心112线程,还不如现在的Zen3——有传闻称最多是80核心160线程,但有待证实,即便如此也不及Zen4。

Hot Chips 33大会上,Intel也重点讲述了Sapphire Rapids,但不是规格参数,而是封装技术,并首次官方展示了实物,而且是去掉顶盖的内部封装,和之前传闻一样是四个Die整合封装在一起。

Intel透露,Sapphire Rapids有两种版本,一个是标准的“SPR XCC”,内部四个Die,每个15核心(开启14个)、面积约400平方毫米,四个Die采用EMIB方式封装在一起,间距55微米,10条连接,封装总面积78×57=4448平方毫米。

另一个是加强型的“SPR HBM”,内部加装四个HBM2E内存,总容量最大64GB,EMIB连接增至14条,封装总面积达100×57=5700平方毫米,增大了约22%。这个版本即便没有DDR5内存也可以独立运行。

相比之下,AMD Genoa的封装面积是5428平方毫米,平均到每个核心大约56.5平方毫米,Intel Sapphire Rapids则是79.4平方毫米。

另外,Intel还透露了Xe HPC高性能计算架构计算卡Ponte Vecchio的更多数据:基础单元面积650平方毫米,整体封装尺寸77.5×62.5=4843.75平方毫米,内部集成八组HBM内存,动用了11个EMIB连接。

它采用了5种不同制造工艺,集成多达47个不同单元,总的晶体管数量超过1000亿个。

-

深圳一男子加油站拔油枪点燃后逃跑 警方已介入调查纵火人员已锁定

头条 21-12-17

-

这位感动千万抖音网友的河南“留虾女孩” 入选央视年度短片《2021看见笑容》

头条 21-12-17

-

泪目!95岁妈妈病床前亲吻74岁生病的女儿 网友:孩子不管多大都是妈妈的宝贝

头条 21-12-15

-

川妹子抽中50颗榴莲直呼吃不完!网友:可以共享你的负担吗?

头条 21-12-15

-

河南省政府发布2022年元旦放假通知

头条 21-12-15

-

濮阳市聚碳新材料产业联盟成立

头条 21-12-15

-

周口机场预计什么时候建好?都有到哪些城市的航线?官方回复来了

头条 21-12-15

-

预计明年超50家企业回归,瑞银称中概股H股上市将继续升温

头条 21-12-15

-

新乡发现一境外输入奥密克戎病例密接者,活动轨迹公布

头条 21-12-15

-

河南:中药配方颗粒不得在医疗机构以外销售

头条 21-12-15

-

中原环保完成发行5亿元超短融,利率2.95%

头条 21-12-15

-

南阳市政府将与中车四方所在新能源装备等领域开展深入合作

头条 21-12-15

-

郑州出台新措施:公租房可“掌上”缴租秒办理

头条 21-12-15

-

国家统计局:11月社会消费品零售总额增长3.9%

头条 21-12-15

-

中国11月规上工业增加值同比增长3.8%

头条 21-12-15

-

1207万!全年就业超额完成预期目标

头条 21-12-15

-

河南凯旺科技公开发行2396万股新股,获6321.47倍申购

头条 21-12-15

-

事关货币政策、房地产、全面注册制,一行两会划定明年工作重点

头条 21-12-15

-

隔夜欧美·12月15日

头条 21-12-15

-

多部委密集部署明年工作!三大看点值得关注

头条 21-12-15

-

立方风控鸟·早报(12月15日)

头条 21-12-15

-

医药巨头今日登陆科创板!高瓴重仓"陪伴",引入"绿鞋"机制

头条 21-12-15

-

皮海洲:临门一脚踏刹车!龙竹科技终止转板说明了什么

头条 21-12-15

-

立方风控鸟·晚报(12月14日)

头条 21-12-14

-

成渝地区双城经济圈建设2022年拟推进160个重大项目,投资约2万亿元

头条 21-12-14

-

总投资额超百亿!中建七局接连中标两个EPC总承包项目

头条 21-12-14

-

2022年部分地方债提前下达,财政提前发力稳经济

头条 21-12-14

-

信阳华信投资集团10亿元中票完成发行,利率3.70%

头条 21-12-14

-

新强联拟择机出售所持明阳智能股票

头条 21-12-14

-

洛阳新强联拟亿元入股山东拟IPO公司,持股4.50%

头条 21-12-14

-

焦作在这场推介会上现场签约28个项目,总投资240亿元

头条 21-12-14

-

河南7种轻微交通违法可免罚

头条 21-12-14

-

广州高校发现古墓考古专业出动!网友:这不巧了嘛!毕业论文自己找来了

头条 21-12-14

-

浙江乐清民警自曝37岁未婚救下轻生女子 网友:一定要最爱自己

头条 21-12-14

-

画面感太强!主人出差猫咪打开水龙头把家淹了 网友:当然是原谅它

头条 21-12-09

-

8岁双胞胎姐妹玩捉迷藏捡到20万摆地摊妈妈报警找失主 网友纷纷点赞

头条 21-12-08

-

女子9楼坠落紧紧抓住7楼防护窗所幸有惊无险!网友:不幸中的万幸啊

头条 21-12-07

-

江西一年级萌娃穿航天服走方阵 网友:可可爱爱的小小航天员

头条 21-12-06

-

女子精心养了半年的盆栽竟是塑料做的 网友:这是做的有多真

头条 21-11-30

-

河南郑州一女子怀上八胞胎!医生一句话说出罕见原因 全家又喜又忧

头条 21-11-26

-

央视新闻AI手语主播正式亮相!网友:专业!第一反应就想到了朱广权

头条 21-11-25

-

网信办:严防违法失德艺人“曲线复出” 营造积极健康向上的网络环境

头条 21-11-24

-

神奇!女子用砂锅煮绿豆粥自动吐皮 网友:这个锅好“懂事”

头条 21-11-23

-

湖南一怀孕老师晕倒学生们立刻化身“闪电侠”飞奔相救

头条 21-11-23

-

26岁癌症女孩刷单被骗23万救命钱 想挣外快结果救命钱打了水漂

头条 21-11-23

-

河南郑州六旬白发教授夜访男寝教微积分:都追到宿舍再学不会就对不起老师

头条 21-11-19

-

男子捡枪上交进门瞬间吓坏警察迅速拔枪警戒 网友:进门倒是说一声啊

头条 21-11-19

-

硬核!男子酒后执意开车被兄弟卸掉轮胎 网友:这才是真朋友啊!

头条 21-11-18

-

撒贝宁时隔4年回归主持今日说法 网友激动喊话:“爷青回”

头条 21-11-18

-

广州一流浪猫被五星级酒店收留凭实力找到长期饭票 每天吃米其林星级员工餐

头条 21-11-17

-

考研冲刺倒计时大学生拿灯管学习?消防员蜀黍顺着网线找来了!

头条 21-11-16

-

经商奇才!长春女子为南方人雪地代写6天赚300元 网友:雪起码得分三成

头条 21-11-16

-

实用又好看!陕西渭南村民在院墙上栽满仙人掌防盗 网友:真的很好看~

头条 21-11-15

-

果农“为国家做研究”捐橘子 网店老板找到了!老板:大家理性消费

头条 21-11-15

-

大乌龙!星空灯下男子捧花告白跪错人 网友:社死现场!

头条 21-11-15

- 北京通州区通报一确诊病例所在的华卿画室未2021-12-20

- 西安全市中小学幼停课!咸阳机场加强防控!2021-12-20

- 香港特区第七届立法会选举 香港各界人士:2021-12-20

- 一次成功的选举,开启香港民主新起点2021-12-20

- 外交部驻港公署:新选制重塑立法会新面貌、2021-12-20

- 国务院港澳办:反中乱港分子及外部支持势力2021-12-20

- 上燃动力20载辉煌,重磅推出新技术、新品牌2021-12-20

- 海南文物艺术品市场日渐繁荣,大唐西市积极2021-11-17

- 中铝国际“六连板” 公司称不涉及盐湖提锂2021-12-20

- 12月基金发行热度再起 年末发行迎来小高峰2021-12-20

- 受上游行情影响进行相关调整 硅片价格继续2021-12-20

- 北向资金周内净买入超百亿 本周7只新股将2021-12-20

- “长安时辰”潮味浓,大唐西市“最唐潮”!2021-08-09

- 2021年医药板块走势“一波三折” 创新生2021-12-20

- 把“蛋糕”做大分好有序推进共同富裕 让发2021-12-20

- 破解“急难愁盼”民生领域改革敲定任务书 2021-12-20

- 农业农村部:逐步补上农村公共服务短板 让2021-12-20

- 全国累计办理制造业中小微企业延缓缴纳税费2021-12-20

- 公开征求意见!证监会拟修订沪伦通规则拓展2021-12-20

- 郑州市交通运输局:2021年底前实现第二绕城2021-12-20

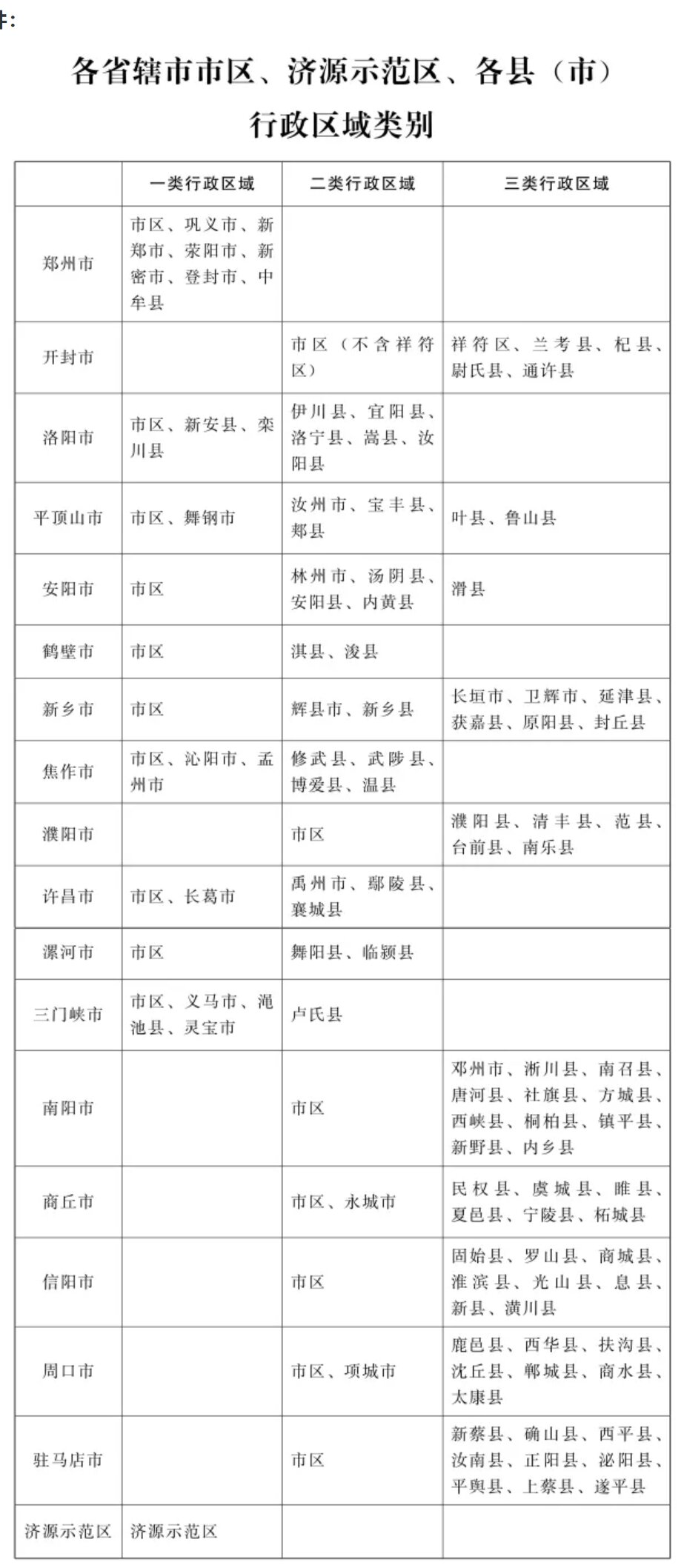

- 河南调整最低工资标准!一类行政区域2000元2021-12-20

- 郑州将迎下半年最冷周末最低气温或跌至-7℃2021-12-20

- 河北省公布义务教育阶段校外培训机构禁止性2021-12-20

- 《南京市中小学生营养午餐指南》(2021版)2021-12-20

- “十四五”我国将大力提高技工待遇 推动高2021-12-20

- 修订后的《高等学校思想政治理论课建设标准2021-12-20

- 内地奥运健儿与澳门青少年运动员开展对话交2021-12-20

- 香港中联办声明:祝贺香港特区第七届立法会2021-12-20

- 今日起 石家庄市区小学生和幼儿上下学免费2021-12-20

- 江西南昌杀妻抛尸案二审维持死刑:被告人主2021-12-20

精彩推荐

阅读排行

- 河南调整最低工资标准!一类行政区域2000元/月小时最低工资标准19.6元

- 降温!暴雪!本周河南气温将出现今年入冬以来最低值 最高气温降至0~2℃

- 河南高纯石英砂提纯技术获突破 提纯二氧化硅纯度达到了99.998%

- 鹤壁辛村遗址发现殷遗民贵族墓葬

- 河南省《通知》 确定175家企业为知识产权强企

- 河南出台《方案》 到2025年公民具备科学素质比例将超15%

- 11月份河南全省经济运行情况发布 新兴动能持续增强经济运行延续恢复态势

- 提醒!河南省2021年度文物勘探许可证年审工作启动

- 河南提前完成惠民惠农财政补贴资金“一卡通”管理全年目标

- 河南发文加快补齐全民健身场地设施短板 探索“体育+公园”新模式